### 5x7mm Precision TCXO Model DV75D

#### **Description:**

The Connor-Winfield's DV75D is a 5x7mm Surface Mount Temperature Compensated Crystal Controlled Oscillator (TCXO) with LVCMOS output. Through the use of Analog Temperature Compensation, the DV75D is capable of holding sub 1-ppm stabilities over the -40 to 85°C temperature range.

#### **Applications:**

GR-253-CORE (SMC) ITU-T-G.813 Option 1 and 2 (SEC)

#

- Features:

- TCXO

- 3.3 Vdc Operation

- LVCMOS Output

- Frequency Stability: ± 1.0 ppm

- Temperature Range: -40 to 85°C

- Low Jitter <1ps RMS</li>

- 5x7mm Surface Mount Package

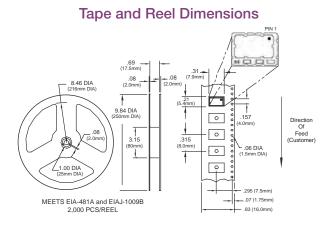

- Tape and Reel Packaging

- RoHS Compliant / Pb Free

#### Absolute Maximum Ratings

| Parameter            | Minimum | Nominal | Maximum | Units | Notes |

|----------------------|---------|---------|---------|-------|-------|

| Storage Temperature  | -55     | -       | 85      | °C    |       |

| Supply Voltage (Vcc) | -0.5    | -       | 6.0     | Vdc   |       |

| Input Voltage        | -0.5    | -       | Vcc+0.5 | Vdc   |       |

| Operating Specifications            |         |                    |         |          |       |

|-------------------------------------|---------|--------------------|---------|----------|-------|

| Parameter                           | Minimum | Nominal            | Maximum | Units    | Notes |

| Nominal Frequency (Fo)              | -       | 10.0, 12.8 or 20.0 | -       | MHz      |       |

| Frequency Calibration @ 25 °C       | -1.0    | -                  | 1.0     | ppm      | 1     |

| Frequency Stability vs. Temperature | -1.0    | -                  | 1.0     | ppm      | 2     |

| Frequency vs. Load Stability        | -0.2    | -                  | 0.2     | ppm      | ±5%   |

| Frequency vs. Voltage Stability     | -0.2    | -                  | 0.2     | ppm      | ±5%   |

| Static Temperature Hysteresis       | -       | -                  | 0.4     | ppm      | 3     |

| Aging                               | -1.0    | -                  | 1.0     | ppm/year |       |

| Operating Temperature Range:        | -40     | -                  | 85      | °C       |       |

| Supply Voltage (Vcc)                | 3.135   | 3.3                | 3.465   | Vdc      | ±5%   |

| Supply Current (Icc)                | -       | -                  | 6       | mA       |       |

| Period Jitter                       | -       | 3                  | 5       | ps rms   |       |

| Integrated Phase Jitter             | -       | 0.5                | 1.0     | ps rms   | 4     |

| Typical Phase Noise Fo = 20.0 MHz   |         |                    |         |          |       |

| SSB Phase Noise at 10Hz offset      | -       | -80                | -       | dBc/Hz   |       |

| SSB Phase Noise at 100Hz offset     | -       | -110               | -       | dBc/Hz   |       |

| SSB Phase Noise at 1KHz offset      | -       | -135               | -       | dBc/Hz   |       |

| SSB Phase Noise at 10KHz offset     | -       | -150               | -       | dBc/Hz   |       |

| SSB Phase Noise at 100KHz offset    | -       | -150               | -       | dBc/Hz   |       |

| Start-up Time                       | -       | -                  | 10      | ms       |       |

#### LVCMOS Output Characteristics

| Parameter                   | Minimum | Nominal | Maximum | Units | Notes |

|-----------------------------|---------|---------|---------|-------|-------|

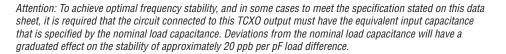

| Load                        | -       | 15      | -       | pF    | 5     |

| Voltage (High) (Voh)        | 90%Vcc  | -       | -       | Vdc   |       |

| (Low) (Vol)                 | -       | -       | 10%Vcc  | Vdc   |       |

| Duty Cycle at 50% of Vcc    | 45      | 50      | 55      | %     |       |

| Rise / Fall Time 10% to 90% | -       | -       | 8       | ns    |       |

#### **Package Characteristics**

|                    | J                                                                 |  |  |  |

|--------------------|-------------------------------------------------------------------|--|--|--|

| Package            | Hermetically sealed crystal mounted on a ceramic package          |  |  |  |

|                    |                                                                   |  |  |  |

|                    | Environmental Characteristics                                     |  |  |  |

| Vibration:         | Vibration per Mil Std 883E Method 2007.3 Test Condition A         |  |  |  |

| Shock:             | Mechanical Shock per Mil Std 883E Method 2002.4 Test Condition B. |  |  |  |

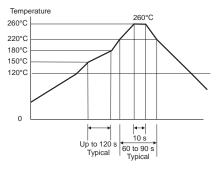

| Soldering Process; | RoHS compliant lead free. See soldering profile on page 2.        |  |  |  |

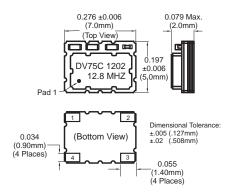

#### Package Layout

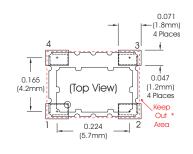

#### Suggested Pad Layout

\* Do not route any traces in the keep out area. It is recommended the next layer under the keep out area is to be ground plane.

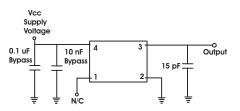

#### Pad Connections .....

| 1: | N/C                  |

|----|----------------------|

| 2: | Ground               |

| 3: | Output (Fo)          |

| 4: | Supply Voltage (Vcc) |

#### **Output Waveform**

#### 0.010"(0.254mm) 50 Ohm trace ecommendi clearance inductance for internal Vcc <1"by design opper flood Buffer Ground Top View Ground Top View 50 Ohm Trace Without Output Vias Buffer TOP LAY GROUND LAYER

BOTTOM LAYER

#### **Test Circuit**

#### **Solder Profile**

Meets IPC/JEDEC J-STD-020C

## **Design Recommendations**

CEOB2B晶振平台-全球最专业的晶振在线采购查询平台http://www.crystal95.com